Essentially the most profitable semiconductor firms know that the rising complexity of built-in circuit (IC) designs is straining our conventional design rule checking (DRC) strategies. The iterative “assemble by correction” method that labored nicely for easier, customized layouts is now creating substantial runtime and useful resource bottlenecks, hindering design groups’ capacity to effectively confirm their superior designs and meet aggressive time-to-market targets. To outpace this design complexity, main semiconductor firms continually search for efficient instruments from its ecosystem companions. Siemens EDA, a serious electronics design automation (EDA) firm supplied a brand new and highly effective shift-left verification technique, they evaluated it and declared it a game-changer for his or her early design phases.

How shift-left addresses the challenges of contemporary IC design

The electronics business is continually on the transfer, innovating and altering elementary features of built-in circuits. Your entire ecosystem reacts and drives enhancements that result in ever sooner, smaller and extra highly effective ICs. For the bodily design and verification of layouts earlier than manufacturing, we may as soon as depend on a handbook, customized course of. This has given approach to extremely automated workflows and multi-layered design hierarchies. As a result of completely different design elements are developed by disparate design groups on completely different timelines, it has grow to be extraordinarily tough to have a totally assembled design structure accessible for complete verification. Moreover, the sheer quantity and complexity of right now’s superior course of design guidelines have exacerbated the runtime and compute necessities for the essential design rule checks (DRC) which can be required earlier than manufacturing.

The answer lies in shifting verification steps earlier within the design course of – a technique referred to as “shift-left” verification. By shifting verification nearer to the supply of design adjustments, shift-left approaches can considerably cut back debug time, handle incomplete information and expedite the trail to tape-out. The runtime and reminiscence distinction between a standard DRC run and a shift-left DRC run is important, as proven in determine 1.

Determine 1. Runtime and reminiscence enhancements of Calibre nmDRC Recon (orange bars) in comparison with Calibre nmDRC (blue bars).Siemens EDA

Main semiconductor firms are having success with the shift-left DRC device from Siemens EDA, known as Calibre DRC Recon. The important thing to this device’s effectiveness lies in its capacity to establish and run solely the principles which can be native in scope, relatively than executing a complete DRC verify throughout the complete design. This “native checks” method drastically reduces runtime and {hardware} necessities in comparison with conventional DRC strategies.

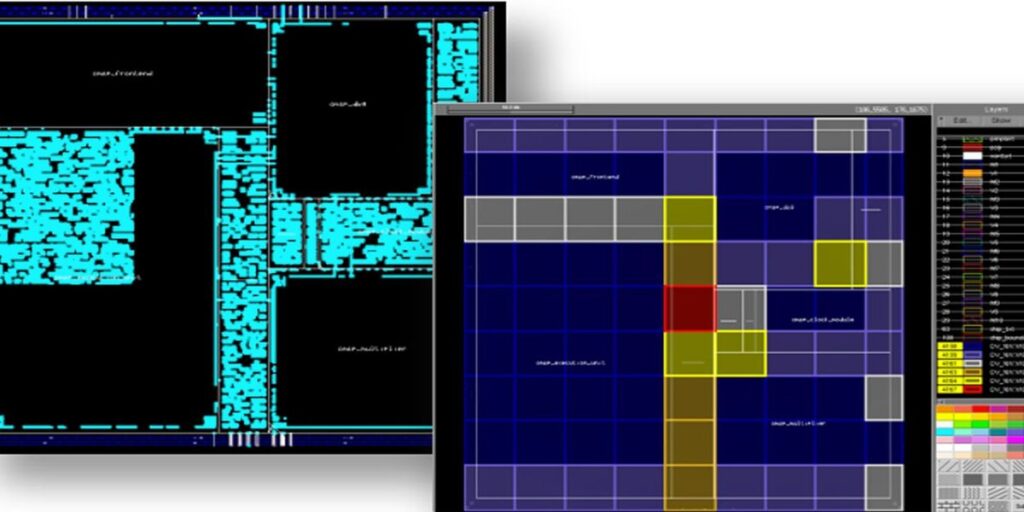

Complementing the native checks method, designers may use an auto-waivers function to establish and exclude areas of the design which can be recognized to be incomplete, eliminating them from checking so false violations don’t decelerate the verification course of. This can be a grey-boxing approach achieved with auto-waivers as illustrated in determine 2.

A buyer’s shift-left DRC success story

A number one expertise firm has seen firsthand the advantages of adopting a shift-left verification technique utilizing Calibre DRC Recon. The design staff was capable of considerably cut back runtime and {hardware} necessities whereas enhancing their general productiveness. The designers began utilizing Calibre nmDRC Recon iterations on the floorplan stage, then on the bodily implementation stage. By that time, a lot of the designs have been clear of shorts on energy and floor nets. They have been capable of catch any points early, whereas they have been nonetheless simple to repair via straight of their structure setting. As a result of these fixes have been made utilizing the sign-off correct Calibre guidelines, the staff knew that the outcomes have been dependable and extremely correct. Determine 3 illustrates runtime enhancements for various DRC strategies.

Determine 3. Run occasions are considerably decreased when utilizing shift-left DRC.Siemens EDA

Determine 3. Run occasions are considerably decreased when utilizing shift-left DRC.Siemens EDA

The designer’s expertise demonstrates the facility of shift-left verification in motion. By leveraging the native checks method and complementary options like auto-waivers and split-deck runs, the staff was capable of speed up their design iterations and cut back time-to-market.

The runtime enhancements have been substantial, with the shift-left DRC device delivering as much as 15 occasions sooner efficiency in comparison with conventional DRC strategies. Furthermore, the reminiscence utilization was decreased by as much as 18 occasions, permitting the design staff to maximise the utilization of their compute sources.

Embracing the shift-left mindset for sooner IC design

Because the complexity of IC designs continues to escalate, design groups can now not depend on conventional DRC strategies to maintain tempo. The shift-left verification technique gives a compelling resolution that addresses the important thing challenges confronted by fashionable design organizations.

By specializing in native checks, leveraging auto-waivers, and optimizing parallel execution, shift-left DRC accelerates the design and verification course of, simplifies debugging and in the end, brings revolutionary merchandise to market sooner. The case examine serves as a robust testomony to the transformative influence of this method, highlighting the numerous productiveness good points and effectivity enhancements that design groups can obtain.

Embracing a shift-left mindset for bodily verification will likely be essential for design groups seeking to keep forward of the curve. The superior DRC device from Siemens EDA gives a confirmed path ahead, equipping designers with the capabilities they should navigate the complexities of contemporary IC design and ship their cutting-edge merchandise to the market with unprecedented velocity and effectivity.